High-Voltage Durable 240-Channel Common Driver for Dot-Matrix STN LCD

# HITACHI

ADE-207-291(Z) Rev. 2 Aug. 03, 1999

## Description

The HD 66137T is a 240-channel common driver which drives a dot matrix STN LCD panel. By changing the mode, this can be applied to 240- and 200- and 160- channel output. Through the use of a 43-V high-voltage CMOS process technology, a high-voltage drive of +21.5 V and -21.5 V, centering on VM is possible. -21.5V generated from +21.5 V with built-in switching circuit and external capacity. Low logic-drive voltage (3 V) is used. This device is used together with the segment driver HD66130, HD66134ST or HD66136.

#### Features

- Display duty: Up to 1/240

- LCD drive voltage: 43 V max

- Built-in switching circuit (to generate –21.5 V)

- Number of LCD drive circuit: 240

- Operating voltage: 2.5 to 5.5 V

- Intermediate voltage I/F

- Built-in alternating signal generation circuit Pin programmable

- Output mode change: 240-output mode

200-output mode

160-output mode

- Built-in display-off function

- Flex TCP

# **Pin Arrangement**

| × × × × × × × × × × × × × × × × × × ×                                                                                                        | X236 | X237<br>V720 | X239<br>X239 | X240  |

|----------------------------------------------------------------------------------------------------------------------------------------------|------|--------------|--------------|-------|

|                                                                                                                                              | 236  | 237          | 239          | 240   |

| Top view                                                                                                                                     |      |              |              |       |

| 273<br>273<br>273<br>272<br>273<br>273<br>264<br>265<br>265<br>265<br>265<br>266<br>265<br>255<br>255<br>255<br>255                          | 245  | 244<br>243   | 242          | 241   |

| VLCDL<br>VHL<br>VHL<br>VLL<br>VLL<br>VLL<br>VLL<br>VLC<br>VLC<br>VLC<br>VLC<br>VMWS3<br>MWS3<br>MWS3<br>MWS3<br>MWS3<br>MWS3<br>MWS3<br>MWS3 | VEER | VLR          | VHR          | VLCDR |

| Note: The shape above does not indicate the actual outline.                                                                                  |      |              |              |       |

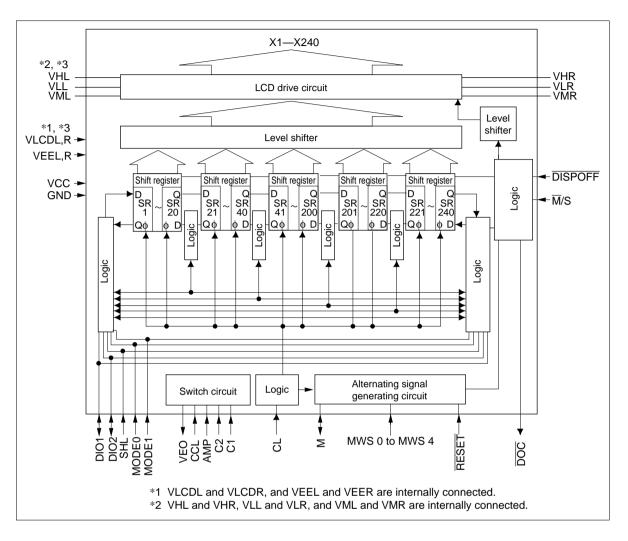

#### **Block Diagram**

## **Internal Block Diagram**

#### 1. LCD drive Circuit

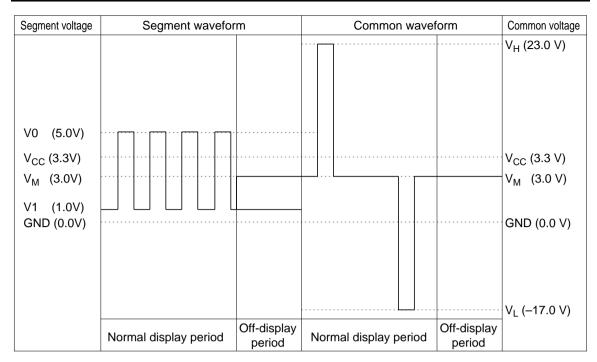

This circuit selects and outputs the three level signals for the LCD drive. By a combination of the data in the shift register and M, either VH, VL, or VM is selected and transmitted to the output circuit.

#### 2. Level shifter

This boosts a 5-V signal to a high-voltage signal for LCD drive.

#### 3. Shift register

This is a 240-bit bidirectional shift register circuit. The first line marker signal output from the DIO1 pin and DIO2 pin is sequentially shifted by shift clock CL. The shift direction is determined by the SHL pin.

#### 4. Alternating signal generating circuit

This circuit generates an alternating signal (M signal) for LCD display. To suppress cross-talk, the signal is alternated in a unit from several lines to several tens of lines. By connecting MWS0 to MWS4 pins to  $V_{CC}$  or GND, the desired number of signals can be alternated. When alternating signals are externally input, all pins (MWS0 to MWS4) are connected to GND.

| HIFAS Fa | mily timing Com | nparison                  |             |

|----------|-----------------|---------------------------|-------------|

|          |                 | HD66130/131S/134S/135/136 | HD66132/133 |

| Input    | CL1             |                           |             |

| signal M | Μ               |                           |             |

| Output   | Segment         |                           | χ           |

| signal   | Common          |                           |             |

## **Pin Function**

| Classification | Symbol                                          | Pin No.                            | Connected<br>to               | I/O    | Functions                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |

|----------------|-------------------------------------------------|------------------------------------|-------------------------------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Power supply   | VLCDL, R<br>VEEL, R<br>V <sub>cc</sub> ,<br>GND | 273, 241<br>269, 245<br>257<br>250 |                               | —      | VLCDL, R–VEEL, R : Power supply for LCD<br>drive<br>VLCDL, R : Power supply for switch circuit<br>$V_{cc}$ –GND : Power supply for logic circuit                                                                                                                                                                                                                                  |  |  |  |  |

|                | VHL, R<br>VLL, R<br>VML, R                      | 272, 242<br>270, 244<br>271, 243   | supply                        | Input  | Power supply for LCD drive level<br>VHL, R : Selected level (Set to the same<br>voltage as VLCDL, R.)<br>VLL, R : Selected level (Set to the same<br>voltage as VEEL, R.)<br>VML, R : Non-selected level and Power<br>supply for switch circuit                                                                                                                                   |  |  |  |  |

|                | VEO                                             | 268                                | VEEL, R                       | output | t When use built -in switching circuit and<br>generate VEE, VEO pin connect to VEEL, R<br>pins. VM voltage is point of reference and<br>reversed and output the voltage input to the<br>voltage between VLCD and VM. If built-in<br>switching circuit is not used, don't connect<br>any lines to this pin.                                                                        |  |  |  |  |

|                | C1, C2                                          | 267, 266                           | Capacitance                   | _      | External capacitance should be connected<br>here when using the switch circuit for<br>generate VEE.<br>If built-in switching circuit is not used, don't<br>connect any lines to this pin.                                                                                                                                                                                         |  |  |  |  |

| Control signal | CL                                              | 249                                | MPU                           | Input  | Shift clock input. Data is shifted at the falling edge of shift clock CL of the shift register.                                                                                                                                                                                                                                                                                   |  |  |  |  |

|                | М                                               | 264                                | Extension<br>driver or<br>MPU | I/O    | Inputs or outputs the alternating current for LCD drive output.                                                                                                                                                                                                                                                                                                                   |  |  |  |  |

|                | MWS0<br>MWS1<br>MWS2<br>MWS3<br>MWS4            | 258<br>259<br>260<br>261<br>262    |                               | Input  | This pin specifies the cycle of the alternating<br>signal (M signal) in the unit of the number of<br>lines. The number of lines, which is an<br>integer from 2 to 31, is specified as follows.<br>Usually, specify the number of lines within a<br>range from 10 to 31. When the HD66131T is<br>driven by an external alternating signal,<br>specify the number of lines as zero. |  |  |  |  |

|                |                                                 |                                    |                               |        | 0   0   0   0   0   0   -   Input     1   0   0   0   1   Prohibited   Output     2   0   0   1   0   2 lines alternated   Output     3   0   0   1   1   3 lines alternated   Input     •   •   •   •   •   •   •     31   1   1   1   1   31 lines alternated   Input                                                                                                           |  |  |  |  |

# **Pin Functions (cont)**

| Classification | Symbol         | Pin No.    | Connected<br>to               | I/O    | Function                                                                                                                                                                                                                                                                                                   |  |  |  |  |

|----------------|----------------|------------|-------------------------------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Control signal | MODE0<br>MODE1 | 256<br>256 | _                             | Input  | Switch terminals for the number of LCD drive output pins.     MODE0 MODE1   Shift direction     "H"   "H"   240 - output (X1, X2, X3X238, X239, X240)     "H"   "L"   200 - output (X21, X22, X23X218, X219, X220)     "L"   "H"   160 - output (X41, X42, X43X198, X199, X200)     "L"   "L"   Prohibited |  |  |  |  |

|                | DIO1<br>DIO2   | 246<br>265 | Extension<br>driver or<br>MPU | I/O    | Serial data input output pin   SHL DIO1 DIO2   "H" level serial output pin serial input pin   "L" level seiral input pin seiral output pin                                                                                                                                                                 |  |  |  |  |

|                | CCL            | 248        | MPU                           | Input  | Built-in switching circuit clock input. When<br>use built-in switching circuit and generate $V_{EE}$ ,<br>this pin connect CL pin.<br>If built-in switching circuit is not used, CCL<br>must be fixed to GND                                                                                               |  |  |  |  |

|                | AMP            | 252        | _                             | Input  | Built-in switching circuit on-off control.<br>When use built-in switching circuit, this pin must be fixed to $V_{cc}$ .<br>If built-in switching circuit is not used, this pin must be fixed to GND                                                                                                        |  |  |  |  |

|                | RESET          | 263        | MPU or $V_{cc}$               | Input  | Setting this pin to GND sets initializes the alternating signal (M signal) circuit. A $V_{cc}$ level RESET is normally used.                                                                                                                                                                               |  |  |  |  |

|                | DISPOFF        | 253        | MPU                           | Input  | Setting this pin to GND sets LCD drive output X1 to X240 to the VM level.                                                                                                                                                                                                                                  |  |  |  |  |

|                | M/S            | 247        | -                             | Input  | M/s DISPOFF pin state and functions   "H" level When DISPOFF is Low level, X1-240 set VM level   "L" level Until serial data input 16 times X1-X240 set VM level                                                                                                                                           |  |  |  |  |

|                | DOC            | 254        | _                             | Output | M/S   DOC     "H" level   When DISPOFF is Low level, output low level<br>When DISPOFF is High level, output High level     "L" level   Until serial data input 16 times output low level<br>from DOC pin     DISPOFF   1 2 3 4 5                                                                           |  |  |  |  |

## **Pin Functions (cont)**

|                     |               |          | Connected |        | _                                         |                                                     |                                         |                                                                                                                       |

|---------------------|---------------|----------|-----------|--------|-------------------------------------------|-----------------------------------------------------|-----------------------------------------|-----------------------------------------------------------------------------------------------------------------------|

| Classification      | Symbol        | Pin No.  | to        | I/O    | Func                                      | tion                                                |                                         |                                                                                                                       |

| Control signal      | SHL           | 251      | _         | Input  | This                                      | pin swite                                           | ches s                                  | hift directions.                                                                                                      |

|                     |               |          |           |        | SHL                                       | MODE0                                               | MODE1                                   | Shift direction                                                                                                       |

|                     |               |          |           |        | "H"                                       |                                                     |                                         | Right shift                                                                                                           |

|                     |               |          |           |        | level                                     | "H"                                                 | "H"                                     | DIO2→SR1······SR240→DIO1                                                                                              |

|                     |               |          |           |        |                                           | "H"                                                 | "L"                                     | DIO2→SR21······SR220→DIO1                                                                                             |

|                     |               |          |           |        |                                           | "L"                                                 | "H"                                     | DIO2→SR41······SR200→DIO1                                                                                             |

|                     |               |          |           |        | "L"                                       |                                                     |                                         | Left shift                                                                                                            |

|                     |               |          |           |        | level                                     | "H"                                                 | "H"                                     | $DIO1 {\rightarrow} SR240 {\cdots} SR1 {\rightarrow} DIO2$                                                            |

|                     |               |          |           |        |                                           | "H"                                                 | "L"                                     | $DIO1 {\rightarrow} SR220 {\cdots} SR21 {\rightarrow} DIO2$                                                           |

|                     |               |          |           |        |                                           | "L"                                                 | "H"                                     | $DIO1 \rightarrow SR200 \cdots SR41 \rightarrow DIO2$                                                                 |

|                     |               |          |           |        | X2•••<br>Note:<br>200-c<br>non-s<br>relea | X240.<br>The 40<br>Dutput o<br>selected<br>se these | ) or 80<br>r 160-<br>l level<br>e pins. | ) correspond to X1,<br>pins invalidated at the<br>output mode output the<br>synchronized every time;                  |

| LCD drive<br>output | X1 to<br>X240 | 1 to 240 | LCD       | Output | By a<br>M sig<br>VH, \<br>the o<br>M      | ynal, who<br>/L, or VI<br>utput cir<br>M            | ation c<br>en DIS<br>M is se<br>rcuit.  | of the display data and the<br>SPOFF is set to $V_{cc}$ , either<br>elected and transmitted to<br>1 0 1 0<br>VM VH VM |

Note: Configuring the LCD panel using the HD66137 when using the select SEGMENT driver.

The Select SEGMENT driver

| SEGMENT driver     | Select |

|--------------------|--------|

| HD66130 (320 OUT)  | 0      |

| HD66132 (240 OUT)  | Х      |

| HD66134S (240 OUT) | 0      |

| HD66136 (400 OUT)  | 0      |

## **Application Example**

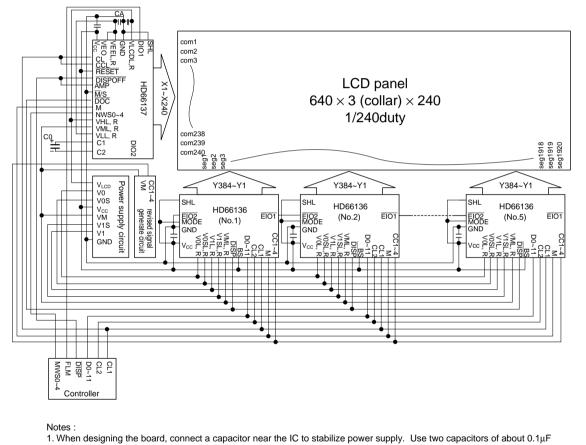

Application Example (1)

Figure 1 shows an application example  $640 \times 3$  (collar)  $\times 240$  dot Half VGA Size STN color panel.

This panel configured HD66137  $\times$  1 piece and HD66136  $\times$  5 pieces.

HD66137 generates M signal and DOC signal. M signal pin is connected M signal pin of HD66136 and DOC signal pin is connected DISP signal pin of HD66136.

HD66137 is able to generates - voltage by external capacitor.

VEO pin is connected VEE pin and VL pin.

for each IC (between Vcc and GND, V0 and GND, VLCD and GND, and VEE and GND).

- 2. In addition, for the power supply circuit, connect a capacitor of several μF or several tens of μF between the liquid-crystal power supply and GND. For set evaluation, confirm that there is no inversion of liquid-crystal drive power supply and level power supply in the period between when the liquid-crystal drive power supply is turned on and when it is turned off.

- 3. When using external capacitor to generate VEE, you must connect a capaciter of several  $\mu$ F or several tens of  $\mu$ F between the VEE and GND.

Figure 1 Application Example (1)

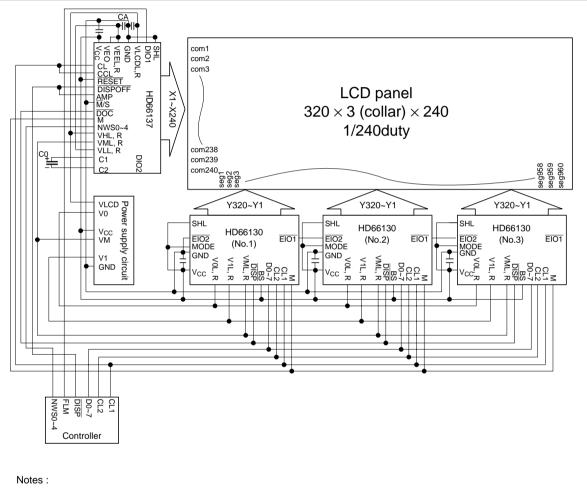

Application Example (2)

Figure 2 shows an application example  $320 \times 3$  (collar)  $\times 240$  dot Quarter VGA Size STN color panel.

This panel configured HD66137  $\times$  1 piece and HD66130  $\times$  3 pieces.

HD66137 generates M signal and DOC signal. M signal pin is connected M signal pin of HD66130 and DOC signal pin is connected DISP signal pin of HD66136.

HD66137 is able to generates - voltage by external capacitor.

VEO pin is connected VEE pin and VL pin.

- 1. When designing the board, connect a capacitor near the IC to stabilize power supply. Use two capacitors of about 0.1µF for each IC (between Vcc and GND, V0 and GND, VLCD and GND, and VEE and GND).

- 2. In addition, for the power supply circuit, connect a capacitor of several µF or several tens of µF between the liquid-crystal power supply and GND. For set evaluation, confirm that there is no inversion of liquid-crystal drive power supply and level power supply in the period between when the liquid-crystal drive power supply is turned on and when it is turned off.

- 3. When useing external capacitor to generate VEE, you must connect a capacitor of several  $\mu$ F or several tens of  $\mu$ F between the VEE and GND.

Figure 2 Application Example (2)

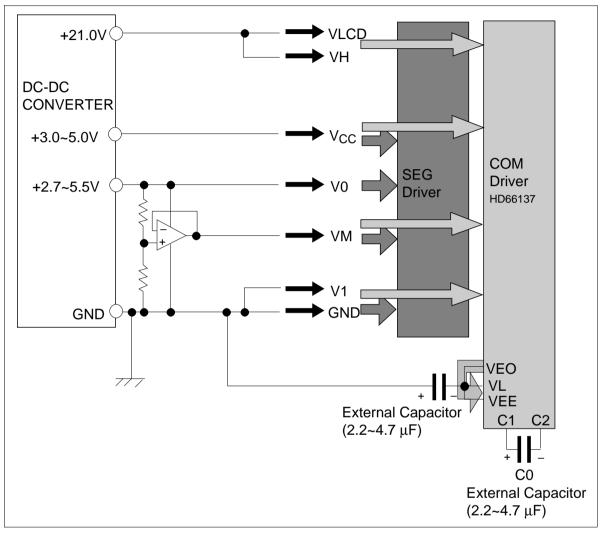

## **Power Supply Circuit Example**

Figure 3 shows a power supply circuit example.

Figure 3 Power Supply Circuit Example

## **Absolute Maximum Rating**

| $V_{cc}$        | -0.3 to +7.0                  | V                                                                                                                                                 | 4.0                                                                                                                                                                           |

|-----------------|-------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                 |                               | v                                                                                                                                                 | 1, 8                                                                                                                                                                          |

| $V_{LCD}$       | -0.3 to +25.0                 | V                                                                                                                                                 | 1, 3, 8                                                                                                                                                                       |

| V <sub>EE</sub> | -20.0 to +0.3                 | V                                                                                                                                                 | 1, 4, 8                                                                                                                                                                       |

| VT1             | -0.3 to V <sub>cc</sub> + 0.3 | V                                                                                                                                                 | 1, 2                                                                                                                                                                          |

| VH              | –0.3 to $V_{\text{LCD}}$      | V                                                                                                                                                 | 1, 5, 8                                                                                                                                                                       |

| VL              | +0.3 to $V_{\text{EE}}$       | V                                                                                                                                                 | 1, 6, 8                                                                                                                                                                       |

| VM              | –0.3 to + 5.0                 | V                                                                                                                                                 | 1, 7, 8                                                                                                                                                                       |

| Topr            | -30 to +75                    | °C                                                                                                                                                |                                                                                                                                                                               |

| Tstg            | –55 to +110                   | °C                                                                                                                                                |                                                                                                                                                                               |

|                 | VT1<br>VH<br>VL<br>VM<br>Topr | $V_{EE}$ -20.0 to +0.3     VT1   -0.3 to $V_{CC}$ + 0.3     VH   -0.3 to $V_{LCD}$ VL   +0.3 to $V_{EE}$ VM   -0.3 to + 5.0     Topr   -30 to +75 | $V_{EE}$ -20.0 to +0.3   V     VT1   -0.3 to $V_{cC}$ + 0.3   V     VH   -0.3 to $V_{LCD}$ V     VL   +0.3 to $V_{EE}$ V     VM   -0.3 to +5.0   V     Topr   -30 to +75   °C |

#### Notes: 1. Voltage from GND.

- 2. Applicable to DIO1, DISPOFF, SHL, M, NWS0, NWS1, NWS2, NWS3, NWS4, RESET, MODE0, MODE1, CL, M/S, AMP, CCL, DIO2.

- 3. Applicable to  $V_{\mbox{\tiny LCDL}},$  R pins.

- 4. Applicable to  $V_{\text{EEL}}$ , R pins.

- 5. Applicable to  $V_{\mbox{\tiny HL}},$  R pins.

- 6. Applicable to  $V_{\scriptscriptstyle LL},\,R$  pins.

- 7. Applicable to  $V_{\mbox{\tiny ML}},$  R pins.

#### (Caution)

Operating the LSI in excess of the absolute maximum rating will result in permanent damage. Use the LSI observing electrical characteristic conditions in normal operation. Exceeding the conditions will cause malfunctions or will affect LSI reliability.

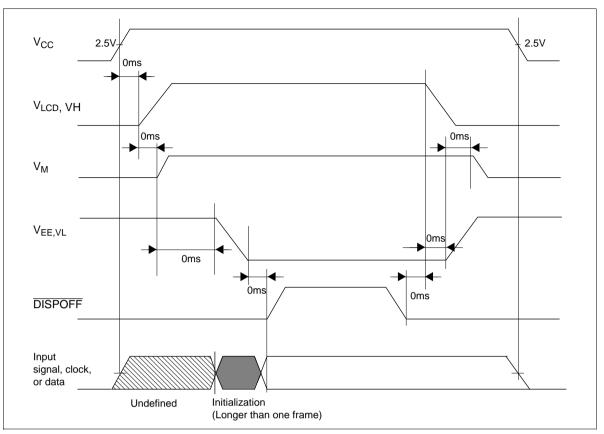

Observe the sequence of activation and inactivation for the following power supplies and signals. And this sequence apply to use built - in switching circuit.

If the sequence is not observed, it may cause LSI malfunction, permanent damage, or adverse effects.

#### 8.1 Power on

- (1) Turn on the power supply in the order of GND-  $V_{cc}$ , GND-VLCD (VH), and VM. VM-VEE is generated automatically. In this case, input GND to the DISPOFF pin.

- (2) The LCD level forcibely outputs the VM level by the DISPOFF function.

- (3) The DISPOFF function has a priority even if input signal distortion occurs immediately after  $V_{cc}$  input.

- (4) Then input the predetermined signals to initialize the driver registers. In this case, assure a period for more than one frame.

- (5) Preparation for normal display is thus completed. Cancel the DISPOFF function by setting the DISPOFF pin to V<sub>cc</sub>. At this point, the levels of VEE (VL), VLCD (VH) and VM must have reached the predetermined respective voltage.

#### 8.2 Shut down

As a rule, shut down in order opposite to that used for power on.

- (1) Set the DISPOFF pin to GND.

- (2) At first shut off the LCD power supply GND-VLCD (VH), at same time GND-VEE (VL) get to VM. Next shut off the VM.

- (3) Set  $V_{cc}$  and the input signal to GND.

At this point, VEE (VL), VLCD (VH) and VM pin input must completely drop to 0 V. Since the DISPOFF function is inactivated when the  $V_{cc}$  level drops to GND, the LCD output may output a level other than VM. Therefore, an incorrect display may appear at shut down or power on.

#### **Electrical Characteristics**

| Item                           | Symbol            | Applicable Pins                                                                                 | Min.                     | Тур. | Max.                | Unit | Measurement<br>Conditions                                                                                                                                                | Notes |

|--------------------------------|-------------------|-------------------------------------------------------------------------------------------------|--------------------------|------|---------------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| Input high-level voltage       | V <sub>IH</sub>   | DIO1, DISPOFF,<br>SHL, M, M/S,<br>MWS0~4, RESET,                                                | $0.7 \times V_{CC}$      | _    | V <sub>cc</sub>     | V    |                                                                                                                                                                          |       |

| Input low-level voltage        | V <sub>IL</sub>   | CL, MODE0,<br>MODE1, DOC,<br>AMP, CCL, DIO2                                                     | 0                        | _    | $0.3 \times V_{CC}$ | V    |                                                                                                                                                                          |       |

| Output high-<br>level voltage  | V <sub>OH</sub>   | M, <u>DOC</u> , DIO1,<br>DIO2                                                                   | V <sub>cc</sub><br>- 0.4 | _    |                     | V    | I <sub>OH</sub> = -0.4 mA                                                                                                                                                |       |

| Output low-<br>level voltage   | V <sub>ol</sub>   | M, <u>DOC</u> , DIO1,<br>DIO2                                                                   | _                        | _    | 0.4                 | V    | I <sub>oL</sub> = 0.4 mA                                                                                                                                                 |       |

| ON resistance<br>between Vi–Yj | RON               | X1 to X240, V pin                                                                               |                          | 0.7  | 2.0                 | kΩ   | I <sub>on</sub> = 150 μA                                                                                                                                                 | 1     |

| Input leak<br>current (1)      | I <sub>LL</sub> 1 | DIO1, DISPOFF,<br>SHL, M, M/S,<br>MWS0~4, RESET,<br>CL, MODE0,<br>MODE1, DOC,<br>AMP, CCL, DIO2 | -5                       | _    | 5                   | μΑ   | $V_{IN} = V_{CC}$ to GND                                                                                                                                                 |       |

| Input leak<br>current (2)      | I <sub>IL</sub> 2 | VH, VL, VM, C1,<br>C2                                                                           | -25                      | _    | 25                  | μA   |                                                                                                                                                                          |       |

| Current<br>consumption (1)     | I <sub>cc</sub> 1 | V <sub>cc</sub>                                                                                 | _                        | 10   | 40                  | μA   |                                                                                                                                                                          | 2     |

| Current<br>consumption (2)     | I <sub>cc</sub> 2 | V <sub>cc</sub>                                                                                 | _                        | 20   | 50                  | μA   | $\begin{split} V_{\rm CC} &= 5.0 \text{ V}, \\ V_{\rm LCD} - V_{\rm EE} &= 40 \text{ V}, \\ f_{\rm CL} &= 19.2 \text{ kHz}, \\ f_{\rm M} &= 1.5 \text{ kHz} \end{split}$ |       |

| Current<br>consumption (3)     | I <sub>LCD</sub>  | V <sub>LCD</sub>                                                                                | _                        | 25   | 50                  | μA   |                                                                                                                                                                          |       |

| <b>DC</b> Characteristics ( $V_{CC} = 2.5$ to | $5.5 V, GND = 0 V, V_{LCD}$ | $V_{EE} = 15$ to 43 V, Ta = -30 to | +75 °C) |

|-----------------------------------------------|-----------------------------|------------------------------------|---------|

|-----------------------------------------------|-----------------------------|------------------------------------|---------|

Notes: 1. This is a resistance value between the X and V pins (either of VH, VL, or VM) when a load current is applied to one of x1 to x240 pins. These values are regulated under the conditions of VLCD = VH = 21.75 V, VEE = VL = −18.5 V, VM = 1.75 V, GND = 0 V, Use VH, VL, and VM in the range of VLCD – VM≥VH – VM = 21.5 to 7.5 V, VEE – VM≤VL – VM = −21.5 to −7.5 V, with the relation of VH > VM > VL.

2. The current applied between the input and output is excluded. When an input to a CMOS gate is at an intermediate level, through current flows between the power supplies, and the power supply current increases. Therefore, use  $V_{IH} = V_{CC}$  and  $V_{IL} = GND$ .

3. The voltage relationship of each signal is as follows :

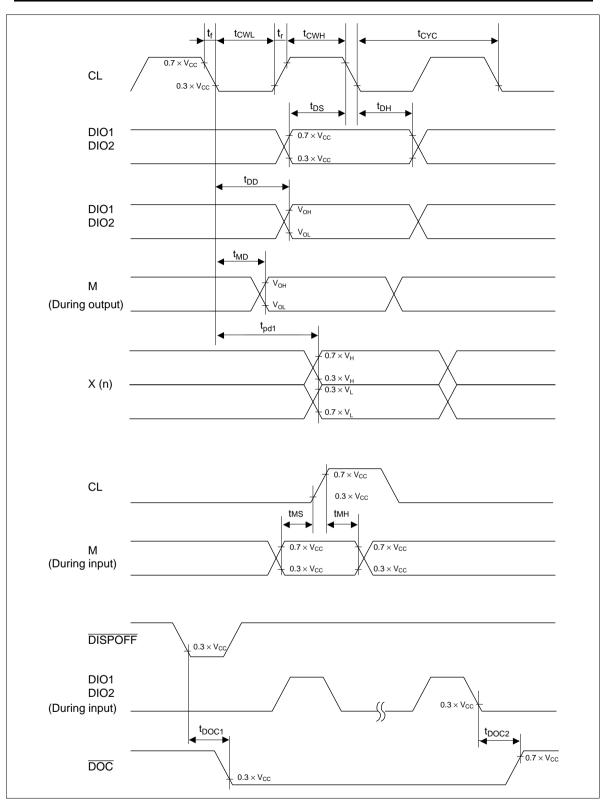

#### AC Characteristics (1) ( $V_{CC}$ = 2.5 to 5.5 V, GND = 0 V, $V_{LCD}$ - $V_{EE}$ = 15 to 43 V, Ta = -30 to +75 °C)

| Item                   | Symbol            | Pin Name                            | min. | max. | Dimensions | Note |

|------------------------|-------------------|-------------------------------------|------|------|------------|------|

| Clock cycle time       | t <sub>cyc</sub>  | CL                                  | 400  | _    | ns         |      |

| CL high-level width    | t <sub>cwH</sub>  | CL                                  | 25   |      | ns         |      |

| CL low-level width     | t <sub>CWL</sub>  | CL                                  | 370  |      | ns         |      |

| CL rising time         | t,                | CL                                  | _    | 30   | ns         |      |

| CL falling time        | t <sub>f</sub>    | CL                                  | _    | 30   | ns         |      |

| Data set-up time       | t <sub>DS</sub>   | DIO1, DIO2, CL                      | 100  | _    | ns         |      |

| Data hold time         | t <sub>DH</sub>   | DIO1, DIO2, CL                      | 10   | _    | ns         |      |

| Data output delay time | t <sub>DD</sub>   | DIO1, DIO2, CL                      |      | 200  | ns         | 1    |

| M output delay time    | t <sub>MD</sub>   | M, CL                               |      | 200  | ns         | 1    |

| M set-up time          | t <sub>MS</sub>   | M, CL                               | 20   | _    | ns         |      |

| M Hold time            | t <sub>MH</sub>   | M, CL                               | 20   |      | ns         |      |

| DOC delay time 1       | t <sub>DOC1</sub> | DISPOFF, DOC                        | _    | 300  | ns         | 2    |

| DOC delay time 2       | t <sub>DOC2</sub> | DIO1, DIO2, $\overline{\text{DOC}}$ | _    | 300  | ns         | 2    |

AC Characteristics (2) ( $V_{CC} = 2.5$  to 4.5 V, GND = 0 V,  $V_{LCD} - V_{EE} = 43$  V, Ta = -30 to +75 °C)

| Item               | Symbol           | Pin Name | min. | max. | Dimensions | Note |

|--------------------|------------------|----------|------|------|------------|------|

| Output delay time1 | t <sub>pd1</sub> | X(n), M  | _    | 1.2  | μs         | 2    |

#### AC Characteristics (3) ( $V_{CC}$ = 4.5 to 5.5 V, GND = 0 V, $V_{LCD}$ - $V_{EE}$ = 43 V, Ta = -30 to +75 °C)

| Item                      | Symbol           | Pin Name           | min.               | max.      | Dimensions | Note |

|---------------------------|------------------|--------------------|--------------------|-----------|------------|------|

| Output delay time1        | t <sub>pd1</sub> | X(n), M            | —                  | 0.7       | μs         | 2    |

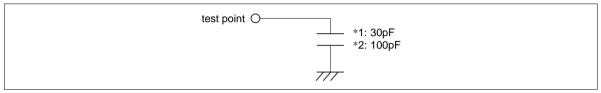

| *1, *2. The following tir | ning is regula   | ated with the circ | uit at the right c | onnected. |            |      |

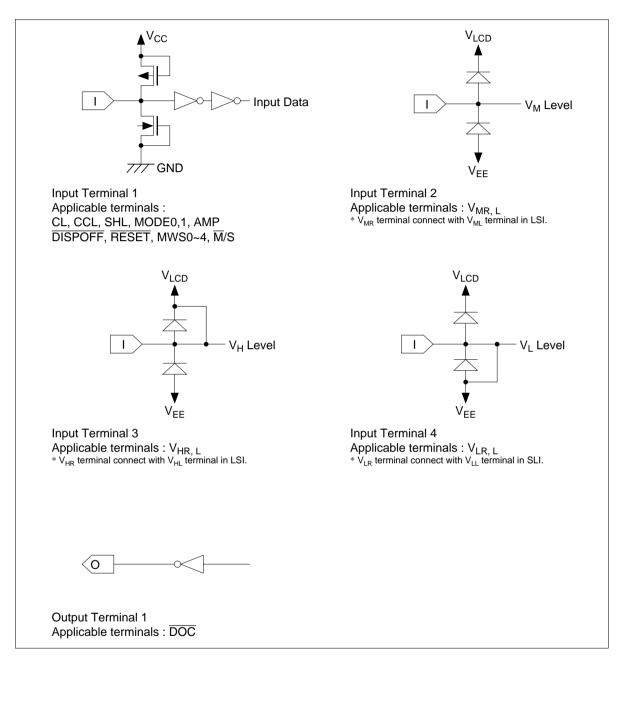

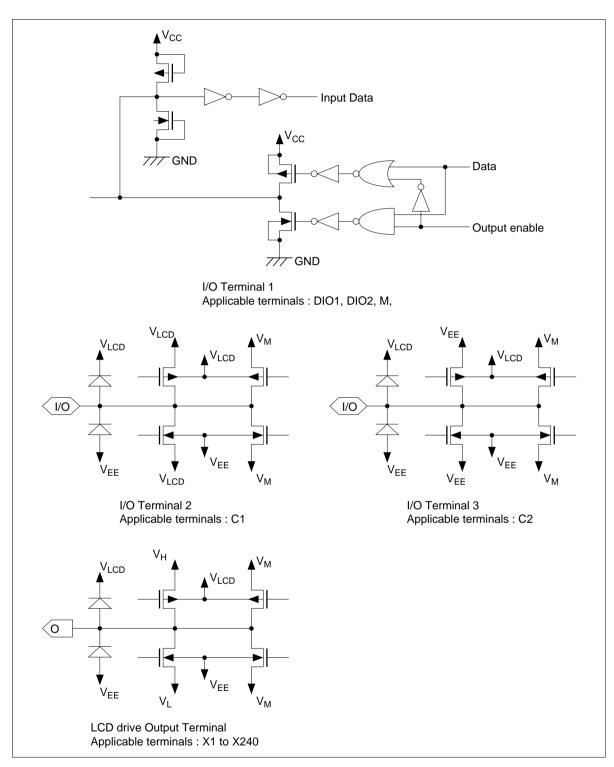

## **Terminal Configuration**

Terminal Configuration (1)

Terminal Configuration (2)

#### Cautions

- 1. Hitachi neither warrants nor grants licenses of any rights of Hitachi's or any third party's patent, copyright, trademark, or other intellectual property rights for information contained in this document. Hitachi bears no responsibility for problems that may arise with third party's rights, including intellectual property rights, in connection with use of the information contained in this document.

- 2. Products and product specifications may be subject to change without notice. Confirm that you have received the latest product standards or specifications before final design, purchase or use.

- 3. Hitachi makes every attempt to ensure that its products are of high quality and reliability. However, contact Hitachi's sales office before using the product in an application that demands especially high quality and reliability or where its failure or malfunction may directly threaten human life or cause risk of bodily injury, such as aerospace, aeronautics, nuclear power, combustion control, transportation, traffic, safety equipment or medical equipment for life support.

- 4. Design your application so that the product is used within the ranges guaranteed by Hitachi particularly for maximum rating, operating supply voltage range, heat radiation characteristics, installation conditions and other characteristics. Hitachi bears no responsibility for failure or damage when used beyond the guaranteed ranges. Even within the guaranteed ranges, consider normally foreseeable failure rates or failure modes in semiconductor devices and employ systemic measures such as fail-safes, so that the equipment incorporating Hitachi product does not cause bodily injury, fire or other consequential damage due to operation of the Hitachi product.

- 5. This product is not designed to be radiation resistant.

- 6. No one is permitted to reproduce or duplicate, in any form, the whole or part of this document without written approval from Hitachi.

- 7. Contact Hitachi's sales office for any questions regarding this document or Hitachi semiconductor products.

# HITACHI Hitachi, Ltd.

| Semiconductor & Integrate<br>Nippon Bldg., 2-6-2, Ohte-r<br>Tel: Tokyo (03) 3270-2111<br>URL NorthAmerica<br>Europe<br>Asia (Singapo<br>Asia (Taiwan)<br>Asia (HongKo<br>Japan | nachi, Chiyoda-ku, Tokyo 100-0004,<br>Fax: (03) 3270-5109<br>a : http:semiconductor.hita<br>: http://www.hitachi-eu.c<br>pre) : http://www.has.hitachi.<br>) : http://www.hitachi.com. | ichi.com/<br>om/hel/ecg<br>com.sg/grp3/sicd/index.htm<br>tw/E/Product/SICD_Frame.htr<br>hk/eng/bo/grp3/index.htm                                                                                                                                                                                   | n                                                                                                                                                                                                                                                                |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| For further informatio<br>Hitachi Semiconductor<br>(America) Inc.<br>179 East Tasman Drive,<br>San Jose,CA 95134<br>Tel: <1> (408) 433-1990<br>Fax: <1>(408) 433-0223          |                                                                                                                                                                                        | Hitachi Asia Pte. Ltd.<br>16 Collyer Quay #20-00<br>Hitachi Tower<br>Singapore 049318<br>Tel: 535-2100<br>Fax: 535-1533<br>Hitachi Asia Ltd.<br>Taipei Branch Office<br>3F, Hung Kuo Building. No.167,<br>Tun-Hwa North Road, Taipei (105)<br>Tel: <886> (2) 2718-3666<br>Fax: <886> (2) 2718-8180 | Hitachi Asia (Hong Kong) Ltd.<br>Group III (Electronic Components)<br>7/F., North Tower, World Finance Centre,<br>Harbour City, Canton Road, Tsim Sha Tsui,<br>Kowloon, Hong Kong<br>Tel: <852> (2) 735 9218<br>Fax: <852> (2) 730 0281<br>Telex: 40815 HITEC HX |

Copyright © Hitachi, Ltd., 1998. All rights reserved. Printed in Japan.